'4D 가우시안 스플래팅'의 하드웨어 가속기 'Relay-GS' 개발

정확도 유지하면서 연산 시간 1.64배 단축…VR·AR 동작 문제 해결

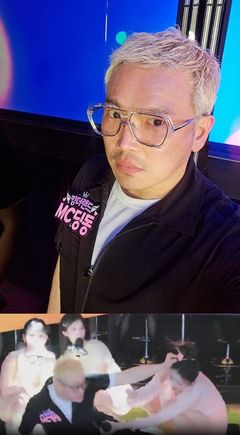

![[서울=뉴시스] (왼쪽 위부터 시계방향으로) 서강대 시스템반도체공학과 류성주 교수, 김영건 석사과정, 전상규· 기성민 석박통합과정생. (사진=서강대 제공) 2026.03.11. photo@newsis.com *재판매 및 DB 금지](https://img1.newsis.com/2026/03/11/NISI20260311_0002081256_web.jpg?rnd=20260311150425)

[서울=뉴시스] (왼쪽 위부터 시계방향으로) 서강대 시스템반도체공학과 류성주 교수, 김영건 석사과정, 전상규· 기성민 석박통합과정생. (사진=서강대 제공) 2026.03.11. [email protected] *재판매 및 DB 금지

[서울=뉴시스]박시은 인턴 기자 = 서강대학교는 시스템반도체공학과·전자공학과 류성주 교수 연구팀의 논문이 반도체 설계 자동화 분야 학술 대회 'DAC(설계 자동화 컨퍼런스·Design Automation Conference) 2026'에 채택됐다고 11일 밝혔다.

'DAC'는 반도체, VLSI(초대규모 집적회로) 설계 및 관련 기술 분야의 발전을 선도해 온 국제 학술대회로, 오는 7월 26일부터 29일까지 미국 롱비치에서 개최될 예정이다.

'4D 가우시안 스플래팅(Gaussian Splatting·4DGS)'는 최근 VR(가상현실)·AR(증강현실) 기기에서 렌더링을 활용한 다양한 인공지능(AI) 애플리케이션에 대해 높은 성능을 보이며 주목받고 있다.

다만 반복적인 가우시안 정렬(Gaussian Sorting) 및 래스터화(Rasterization) 과정에서 발생하는 막대한 계산량과 에너지 소비가 실시간 응용에 걸림돌로 작용했다.

연구팀은 이를 해결하고자 해당 과정에서 타임스텝(Timestep) 간 상당한 유사성이 있음을 분석했다. 이를 활용해 정확도를 최대한 유지한 채 연산을 경량화하는 방법을 적용한 4DGS 하드웨어 가속기 '릴레이(Relay)-GS'를 개발했다.

실험 결과, 개발된 '릴레이-GS'는 기존 4DGS 모델과 유사한 수준의 정확도를 유지하면서도 기존 하드웨어 가속기 대비 4DGS 연산 시간을 최대 1.64배 단축하는 성과를 거뒀다.

김영건 석사과정 학생의 주도하에 기성민·전상규 석박사통합과정생이 함께 진행한 이번 연구는 VR·AR 기기 동작의 높은 연산 비용과 지연 시간 문제 해결에 이바지할 것으로 평가된다.

◎공감언론 뉴시스 [email protected]

'DAC'는 반도체, VLSI(초대규모 집적회로) 설계 및 관련 기술 분야의 발전을 선도해 온 국제 학술대회로, 오는 7월 26일부터 29일까지 미국 롱비치에서 개최될 예정이다.

'4D 가우시안 스플래팅(Gaussian Splatting·4DGS)'는 최근 VR(가상현실)·AR(증강현실) 기기에서 렌더링을 활용한 다양한 인공지능(AI) 애플리케이션에 대해 높은 성능을 보이며 주목받고 있다.

다만 반복적인 가우시안 정렬(Gaussian Sorting) 및 래스터화(Rasterization) 과정에서 발생하는 막대한 계산량과 에너지 소비가 실시간 응용에 걸림돌로 작용했다.

연구팀은 이를 해결하고자 해당 과정에서 타임스텝(Timestep) 간 상당한 유사성이 있음을 분석했다. 이를 활용해 정확도를 최대한 유지한 채 연산을 경량화하는 방법을 적용한 4DGS 하드웨어 가속기 '릴레이(Relay)-GS'를 개발했다.

실험 결과, 개발된 '릴레이-GS'는 기존 4DGS 모델과 유사한 수준의 정확도를 유지하면서도 기존 하드웨어 가속기 대비 4DGS 연산 시간을 최대 1.64배 단축하는 성과를 거뒀다.

김영건 석사과정 학생의 주도하에 기성민·전상규 석박사통합과정생이 함께 진행한 이번 연구는 VR·AR 기기 동작의 높은 연산 비용과 지연 시간 문제 해결에 이바지할 것으로 평가된다.

◎공감언론 뉴시스 [email protected]