삼성전자·인텔 추격에도 신기술 앞세워 시장 선점

초대형 고집적 패키징 'SoW-X' 주목…2027년 양산

[서울=뉴시스]이인준 기자 = TSMC가 인공지능(AI) 반도체 시장을 겨냥한 차세대 공정과 최첨단 패키징 기술을 공개해 업계의 주목을 받고 있다.

TSMC를 향한 삼성전자, 인텔 등 글로벌 반도체 기업들의 도전이 지속되고 있지만, 새로운 기술을 통해 시장 주도권을 이어가겠다는 전략으로 풀이된다.

25일 업계에 따르면 TSMC는 지난 23일(현지시간) 미국 캘리포니아 산타클라라에서 열린 TSMC 테크놀로지 심포지엄에서 1.4나노미터(㎚·10억분의 1m) 공정인 'A14'를 공개했다.

이 공정은 TSMC가 올해 하반기 양산 예정인 N2(2나노) 공정 대비 성능은 최대 15% 향상되고, 전력 효율은 30% 높아졌다. 칩의 집적도도 20% 이상 높아져, 같은 면적에 더 많은 기능을 넣을 수 있게 됐다. 또 전력 효율성을 높인 2세대 GAA(게이트올어라운드)의 나노시트 트랜지스터를 기반으로 설계됐다.

TSMC는 올해 하반기 2나노 공정 양산과 내년 하반기 A16 공정에 이어 새로운 공정인 A14을 2028년까지 선보이며 경쟁 업체들과 격차를 벌리는 전략을 이어갈 것으로 보인다. 또 2029년에는 후면전력전달(BSPD) 기술을 처음 도입한 A14B 공정도 선보일 계획이다.

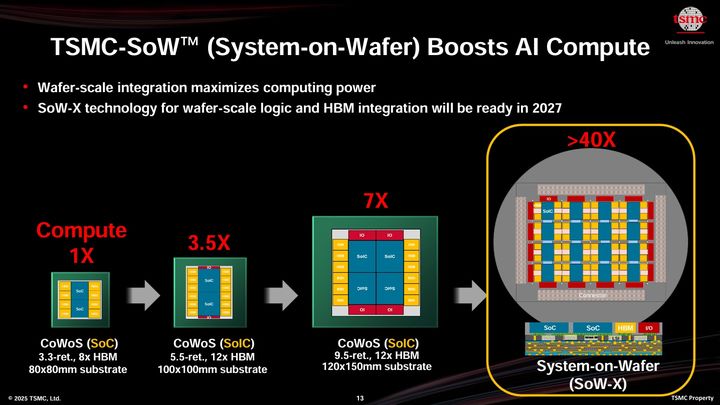

이와 함께 초대형 고집적 패키징 기술인 '시스템온웨이퍼(System-on-Wafer X·SoW-X)'도 처음 공개했다.

TSMC는 서로 다른 칩을 하나의 기판 위에 효율적으로 연결해, 포장(패키징)하는 CoWoS(Chip-on-Wafer-on-Substrate)로 AI(인공지능) 반도체 시장을 장악하고 있다.

TSMC는 여기서 한 발 더 나아가 단일 패키지를 넘어 웨이퍼 단위에서 칩을 통합하는 기술을 개발하고 있다고 밝혔다.

이 기술을 이용하면 최대 16개 이상의 고성능 컴퓨팅 칩과 메모리, 광통신 인터페이스를 하나로 연결할 수 있다.

현재 엔비디아의 AI 반도체에 들어가는 GPU(그래픽처리장치)는 2개를 묶은 형태로 들어가며, 2027년 하반기 양산되는 루빈 넥스트부터는 4개의 GPU를 하나로 엮는다. 이를 고려하면 'SoW-X'는 현재 CoWoS 솔루션 대비 40배 컴퓨팅 성능을 갖춘 웨이퍼 크기의 시스템을 만들 수 있다.

특히 현재 칩 한 개당 8~12개 수준인 HBM(고대역폭메모리)의 개수도 대폭 늘어날 수 있게 된다. TSMC는 이 기술에 HBM4를 사용할 계획이며, 실리콘 포토닉스(반도체에 빛을 활용해 데이터 전송 및 처리 속도를 높이는 기술) 등도 적용한다. 그러면서도 수천와트(W)의 전력 공급이 가능하도록 설계돼, 차세대 AI 학습 및 추론용 칩의 전력·열관리 한계를 극복할 수 있다는 평가를 받는다.

TSMC는 SoW-X를 2027년 대량 생산한다고 밝혔다. 이를 본격화하기 위해 미국 애리조나에 2개의 패키징 전용 공장을 신설할 계획이다. 이는 기존 6개 반도체 팹(제조 공장)과 함께 운영되며 단지 내에는 연구개발센터도 조성된다. 엔비디아, AMD 등 미국 내에서 급격하게 늘고 있는 첨단 패키징 수요에 대응하기 위한 전략으로 보인다.

◎공감언론 뉴시스 [email protected]