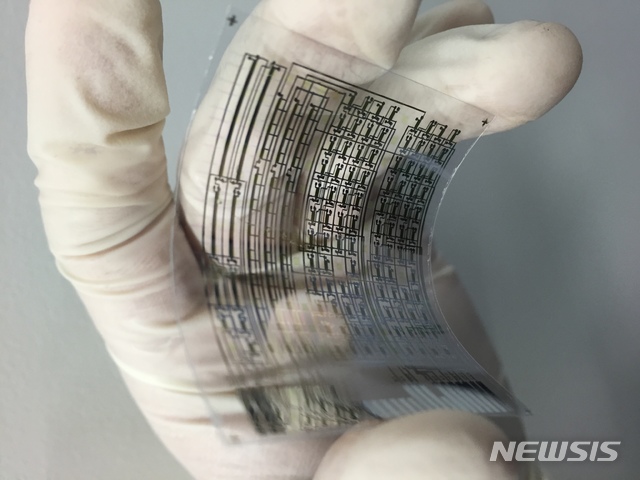

【포항=뉴시스】강진구 기자 = 포스텍(총장 김도연)은 창의IT융합공학과 정성준(사진) 교수·권지민 박사, 화학공학과 조길원 교수팀이 일본 야마가타 대학교 토키토 교수 연구진과의 협업을 통해 3D 프린팅 기술을 사용해 플렉시블(유연)한 플라스틱 기판 위에 인쇄된 반도체 소자를 지속적으로 쌓아 올려 세계 최고 집적도의 인쇄형 플렉시블 반도체 회로를 구현하는 데 성공했다고 30일 밝혔다.2019.01.30.(사진=포스텍 제공) [email protected]

【포항=뉴시스】강진구 기자 = 포스텍(총장 김도연)은 창의IT융합공학과 정성준 교수·권지민 박사, 화학공학과 조길원 교수팀이 일본 야마가타 대학교 토키토 교수 연구진과 협업을 통해 3D 프린팅 기술을 사용해 플렉시블(유연)한 플라스틱 기판 위에 인쇄된 반도체 소자를 지속적으로 쌓아 올려 세계 최고 집적도의 인쇄형 플렉시블 반도체 회로를 구현하는 데 성공했다고 30일 밝혔다.

소비전력을 낮추고 최대 전류를 높이는 등으로 인쇄형 트랜지스터 성능을 극대화하는 기술을 활용했다고 덧붙였다.

그동안 유기 반도체 분야는 트랜지스터 사이즈가 크고 집적도가 낮아 상용화에 어려움이 있어 왔다.

이에 연구팀은 단 하나의 게이트로 이뤄진 단일 박막트랜지스터를 평면적으로 인쇄해 집적도가 낮다는 데 착안해 세계 최초로 서로 돕는 양방향 구조의 듀얼 게이트 트랜지스터를 3차원으로 쌓아 올려 다양한 3차원의 디지털 논리회로를 제작했다.

이 듀얼 게이트 소자구조를 도입하면 인쇄형 트랜지스터의 성능이 극대화되면서 게이트를 하나만 사용했을 때에 비해 2배이상의 전류가 흐르고 동작이 빨라지는 등 효율이 향상된다.

이 같은 3차원 적층 기법을 통해 플라스틱 위에 전자소자와 회로를 쌓으면 반도체의 집적도를 비약적으로 높일 수 있어 많은 수의 트랜지스터가 필요한 유연 전자 회로의 상용화에 크게 기여할 수 있을 것으로 기대된다.

소비전력을 낮추고 최대 전류를 높이는 등으로 인쇄형 트랜지스터 성능을 극대화하는 기술을 활용했다고 덧붙였다.

그동안 유기 반도체 분야는 트랜지스터 사이즈가 크고 집적도가 낮아 상용화에 어려움이 있어 왔다.

이에 연구팀은 단 하나의 게이트로 이뤄진 단일 박막트랜지스터를 평면적으로 인쇄해 집적도가 낮다는 데 착안해 세계 최초로 서로 돕는 양방향 구조의 듀얼 게이트 트랜지스터를 3차원으로 쌓아 올려 다양한 3차원의 디지털 논리회로를 제작했다.

이 듀얼 게이트 소자구조를 도입하면 인쇄형 트랜지스터의 성능이 극대화되면서 게이트를 하나만 사용했을 때에 비해 2배이상의 전류가 흐르고 동작이 빨라지는 등 효율이 향상된다.

이 같은 3차원 적층 기법을 통해 플라스틱 위에 전자소자와 회로를 쌓으면 반도체의 집적도를 비약적으로 높일 수 있어 많은 수의 트랜지스터가 필요한 유연 전자 회로의 상용화에 크게 기여할 수 있을 것으로 기대된다.

【포항=뉴시스】강진구 기자 = 포스텍(총장 김도연)은 창의IT융합공학과 정성준 교수·권지민 박사, 화학공학과 조길원 교수팀이 일본 야마가타 대학교 토키토 교수 연구진과의 협업을 통해 3D 프린팅 기술을 사용해 플렉시블(유연)한 플라스틱 기판 위에 인쇄된 반도체 소자를 지속적으로 쌓아 올려 세계 최고 집적도의 인쇄형 플렉시블 반도체 회로를 구현하는 데 성공했다고 30일 밝혔다.사진은 포스텍 연구진이 구현한 인쇄형 플렉시블 반도체 회로.2019.01.30.(사진=포스텍 제공) [email protected]

2년마다 반도체 집적도가 2배 증가한다는 실리콘 트랜지스터 분야의 무어의 법칙처럼 인쇄형 박막트랜지스터에서도 지속적으로 집적도 증가를 이룰 수 있음도 증명해 냈다.

공정 온도가 낮아 비용도 적게 들고 웨어러블 전자 기기에 빠르고 쉽게 활용이 가능해 이 분야 상용화에도 도움을 줄 것으로 기대된다.

이번 연구 결과는 네이처 자매지 네이처 커뮤니케이션즈(Nature Communications)에 최근호에 게재됐다.이 연구는 과학기술정보통신부의 IT명품인재양성사업과 글로벌프론티어사업, 나노 기반 소프트일렉트로닉스 센터의 지원을 받아 수행됐다.

정성준 교수는 “차세대 기술 중 하나로 손꼽히고 있는 인쇄형 플렉시블 박막 트랜지스터를 3차원으로 집적하는 데 성공했다”며 “이를 통해 인쇄형 반도체의 지속적 기술성장 계기를 세계 최초로 증명해 냈다”고 연구의 의의를 밝혔다.

[email protected]

공정 온도가 낮아 비용도 적게 들고 웨어러블 전자 기기에 빠르고 쉽게 활용이 가능해 이 분야 상용화에도 도움을 줄 것으로 기대된다.

이번 연구 결과는 네이처 자매지 네이처 커뮤니케이션즈(Nature Communications)에 최근호에 게재됐다.이 연구는 과학기술정보통신부의 IT명품인재양성사업과 글로벌프론티어사업, 나노 기반 소프트일렉트로닉스 센터의 지원을 받아 수행됐다.

정성준 교수는 “차세대 기술 중 하나로 손꼽히고 있는 인쇄형 플렉시블 박막 트랜지스터를 3차원으로 집적하는 데 성공했다”며 “이를 통해 인쇄형 반도체의 지속적 기술성장 계기를 세계 최초로 증명해 냈다”고 연구의 의의를 밝혔다.

[email protected]